Version: A

2015-09-25

# Specification for Approval

| Customer:   |  |

|-------------|--|

| Model Name: |  |

| S            | upplier Approva | Customer approval |  |

|--------------|-----------------|-------------------|--|

| R&D Designed | R&D Approved    | QC Approved       |  |

| Peter        | Peng Jun        |                   |  |

Version: A

2015-09-25

### 1. Revision Record

| REV NO. | REV DATE   | CONTENTS  | Note |

|---------|------------|-----------|------|

| A       | 2015-09-25 | NEW ISSUE |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

|         |            |           |      |

Version: A

2015-09-25

## 2. Table of Contents

| List | Description                                 | Page No. |

|------|---------------------------------------------|----------|

|      | Cover                                       | 1        |

| 1    | Revision Record                             | 2        |

| 2    | Table of Contents                           | 3        |

| 3    | Scope                                       | 4        |

| 4    | Product Information                         | 5        |

| 5    | Absolute Maximum Ratings                    | 6        |

| 6    | Electrical Specification                    | 6        |

| 7    | Optical Specification                       | 8        |

| 8    | Viewing Modes                               | 8        |

| 9    | Electro-Optical Characteristics Test Method | 9        |

| 10   | Outline Dimension                           | 10       |

| 11   | Table of Pin Assignment                     | 11       |

| 12   | MIPI-DSI interface                          | 12       |

| 13   | Reliability                                 | 13       |

| 14   | Packaging                                   | 14       |

Version: A

2015-09-25

### 3. Scope

This specification defines general provisions as well as inspection standards for TFT module supplied by AMSON electronics.

If the event of unforeseen problem or unspecified items may occur, naturally shall negotiate and agree to solution.

Version: A

2015-09-25

#### 4. PRODUCT INFORMATION

#### 4.1. Description

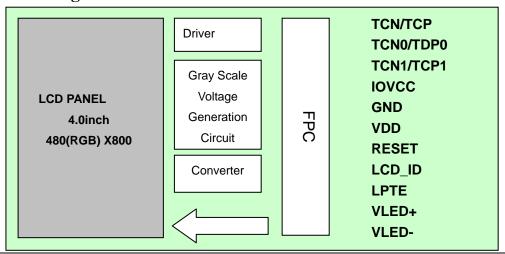

DBT040TS02A is a color active matrix LCD module incorporating amorphous silicon TFT(Thin Film Transistor). It is composed of a color TFT-LCD panel, driver ICs, FPC and a backlight unit. The 4.0" display area contains 480(RGB) x 800pixels and can display up to 16.7M colors.

#### 4.2. Applications

UMPC

Digital photo frame

GPS

#### 4.3. Features

High Resolution: 480(RGB) x 800 Dots Panel Size:4.0(16:9 diagonal) inch

Interface: MIPI 8 LED backlight

#### 4.4. General Specifications

| Item                     | Specification                | Unit    | Remark |

|--------------------------|------------------------------|---------|--------|

| Display Mode             | Normally Black               | -       | -      |

| <b>Outline Dimension</b> | 57.14(H) X 96.85(V) X2.05(T) | mm      | -      |

| Active Area              | 51.84(H) x86.40 (V)          | mm      | -      |

| Resolution               | 480X(RGB)X800                | dots    | -      |

| Pixel Pitch              | 108X108                      | μm      | -      |

| Pixel Configuration      | RGB Stripe                   | 1       | -      |

| Weight                   | TBD                          | g       | -      |

| Luminance                | 400 (TYP)                    | cd/m2   | -      |

| Signal Interface         | MIPI                         | -       | -      |

| Viewing Direction        | Free                         | o'clock | Note   |

#### 4.5. <Block diagram>

Version: A

2015-09-25

#### 5. ABSOLUTE MAXIMUM RATINGS

| Item                               | Symbol  | Condition | Min  | Max | Unit         |

|------------------------------------|---------|-----------|------|-----|--------------|

| Logic supply voltage               | VDD3    | Ta= 25℃   | -0.3 | 4.6 | V            |

| Supply voltage for step-up circuit | VCI     | Ta= 25℃   | -0.3 | 4.6 | V            |

| LCD supply voltage range           | VGH-VGL | Ta= 25℃   | -0.3 | 32  | V            |

| Operating temperature              | Тора    | Ta= 25℃   | -20  | 65  | $^{\circ}$ C |

| Storage temperature                | Tstg    | Ta= 25℃   | -40  | 85  | $^{\circ}$ C |

| Storage humidity                   | Hstg    | Ta= 25℃   | 10   | 90  | %            |

#### Note:

### 6. ELECTRICAL SPECIFICATIONS (Ta=25°C)

#### 6.1. DC CHARACTERISTICS

Recommend Parameters for Electrical Characteristics

| Item          | 1                   | Symbol  | Unit | Min.       | Тур. | Max.       | Remark |  |

|---------------|---------------------|---------|------|------------|------|------------|--------|--|

| T             | Input power supply  |         | ٧    | 1.65       | 1.8  | 3.3        | Note 1 |  |

| Input power   |                     |         | V    | 2.5        | 2.8  | 3.3        | Note 1 |  |

|               | MIPI I/F            | Idd+Ici | mA   | -          | 1    | 35         | Note 2 |  |

| Current       |                     | Islp    | uA   | -          | -    | 250        | -      |  |

| Spec          | RGB I/F             | Idd+Ici | mA   | -          | -    | 35         | -      |  |

|               | ROD 1/1             | Islp    | uA   | -          | -    | 150        | -      |  |

| Frame         | MIPI I/F<br>RGB I/F | Hz      |      | -          | 60   | 70         | Note 3 |  |

| Input Signal  | H Level             | VIH     | V    | 0.7 x VDD3 | -    | VDD3       | _      |  |

| Voltage       | L Level             | VIL     | V    | 0          | -    | 0.3 x VDD3 |        |  |

| Output signal | H Level             | VOH     | V    | 0.8 x VDD3 | -    | VDD3       | _      |  |

| Voltage       | L Level             | VOL     | V    | 0          | -    | 0.2 x VDD3 | _      |  |

| I DI ECD      |                     | HBM     | kV   | -2         | -    | +2         | _      |  |

| LDI ES        | טט                  | MM      | V    | -200       | -    | +200       | _      |  |

<sup>\*1)</sup> If the module exceeds the absolute maximum ratings, it may be damaged permanently. Also, if the module operated with the absolute maximum ratings for a long time, its reliability may drop. It is not allowed for any of these ratings to be exceeded. Make sure all the design characteristics are adequate before the panel is initialed.

<sup>\*2)</sup> All the measurements should be operated with driver IC and experimental FPC mounted.

Version: A

2015-09-25

#### Note:

- \*1) The operation is guaranteed under the recommended operating conditions only. The operation is not guaranteed if a quick voltage change occurs during operation. To prevent noise, a bypass capacitor must be inserted into the line close to power pin. Please make sure all the design settings are used within this range before the panel is initialed

- \*2) Please make sure that DC is not supplied to LCD for long period. And do not supply voltage to LCD while within "sleep mode".

- \*3) All the measurements should be operated with driver IC and experimental FPC.

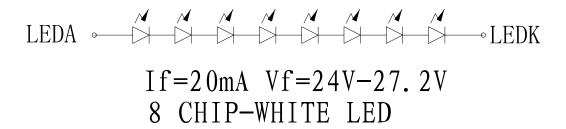

#### 6.2. Backlight Driving Section

#### 6.3. BACKLIGHT CHARACTERISTICS

| Parameter                      |    | Min.  | Typ.  | Max. | Unit | Remarks |

|--------------------------------|----|-------|-------|------|------|---------|

| LED Forward Voltage            | VF | 24    | 25.6  | 27.2 | V    | -       |

| <b>LED Forward Current</b>     | IF | -     | 20    |      | mA   | -       |

| <b>Operating LED life time</b> | Hr | 20000 | 40000 |      | Hour | (1)     |

Remarks (1) The "LED life time" is defined as the module brightness decrease to 50% original brightness at Ta=25℃ and IF=240mA.

Version: A

2015-09-25

### 7. OPTICAL SPECIFICATIONS(Ta=25°C)

| Iter         | n                 | Symbol | Min.  | Тур.  | Max.  | Unit    | Remarks              |

|--------------|-------------------|--------|-------|-------|-------|---------|----------------------|

| Threshold    | Threshold Voltage |        | 4.1   | 4.3   | 4.5   | V       |                      |

| Inresnoia    | voitage           | Vth    | 1.6   | 1.8   | 2.0   | V       |                      |

| Contrast     | Ratio             | C/R    | 650   | 900   | 1300  |         | Fig.1                |

| Bright       | noce              |        | 350   | 400   |       | cd/m2   | Full White Pattern   |

| Dright       | 11688             | -      | 330   | 400   | -     | - Cu/mz | (Transmittance 7.4%) |

| NTS          | SC                | %      | 65%   | 70%   | 75%   |         |                      |

| Brightness U | Iniformity        |        | 80    | -     | -     | %       | Full White Pattern   |

| Response     | e Time            | Tr+Tf  | ı     | 35    | 42    | ms      | Fig.3                |

| Color        | WHITE             | Wx     | 0.268 | 0.288 | 0.308 |         | IBL=20mA             |

| Coordinate   | WIIIIE            | Wy     | 0.299 | 0.319 | 0.339 |         | Full White Pattern   |

|              |                   | θl     | 70    | 85    | -     |         | Fig.4                |

| view angle   |                   | θr     | 70    | 85    | -     | Degree  | Center               |

|              |                   | θu     | 70    | 85    | -     |         | (C/R>10)             |

|              |                   | θd     | 70    | 85    | -     |         |                      |

#### Note:

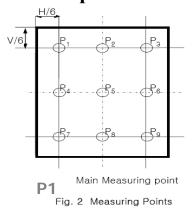

1. Contrast Ratio(CR) is defined mathematically as:

Surface Luminance with all white pixels

Contrast Ratio = Surface Luminance with all black pixels

2. Surface luminance is the center point across the LCD surface 500mm from the surface with all

pixels displaying white. For more information see FIG 1.

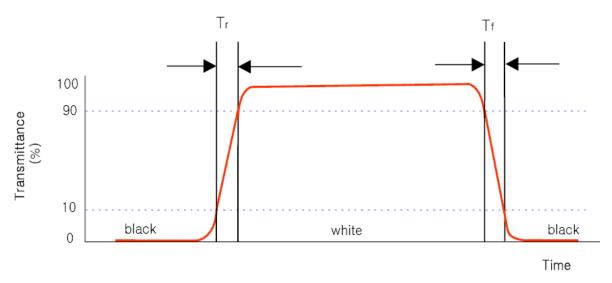

3. Response time is the time required for the display to transition from black to white (Rise Time, Tr) and from white to black(Decay Time, Tf). For additional information see FIG 3.

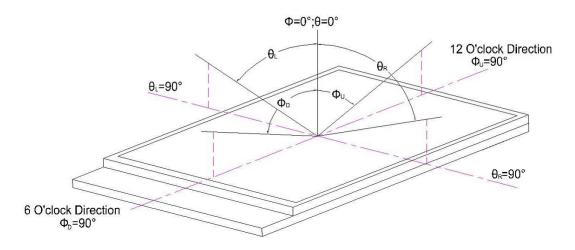

4. Viewing angle is the angle at which the contrast ratio is greater than 5. The angles are

determined for the horizontal or x axis and the vertical or y axis with respect to the z axis which is normal to the LCD surface. For more information see FIG 4.

5. Optimum contrast is obtained by adjusting the LCD Threshold voltage (Vth& Vsat)

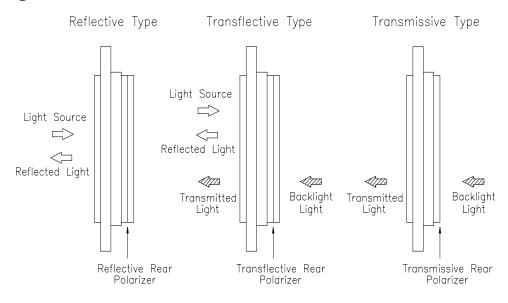

### 8. Viewing Modes

Version: A

2015-09-25

## 9. Electro-Optical Characteristics Test Method

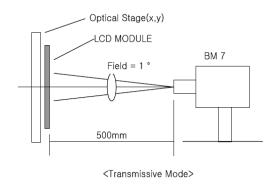

FIG. 1 Optical Characteristic Measurement Equipment and Method

The response time is defined as the following figure and shall be measured by switching the input signal for "black" and "white".

FIG.3 The definition of Response Time

FIG.4 The definition of Viewing Angle

Version: A

2015-09-25

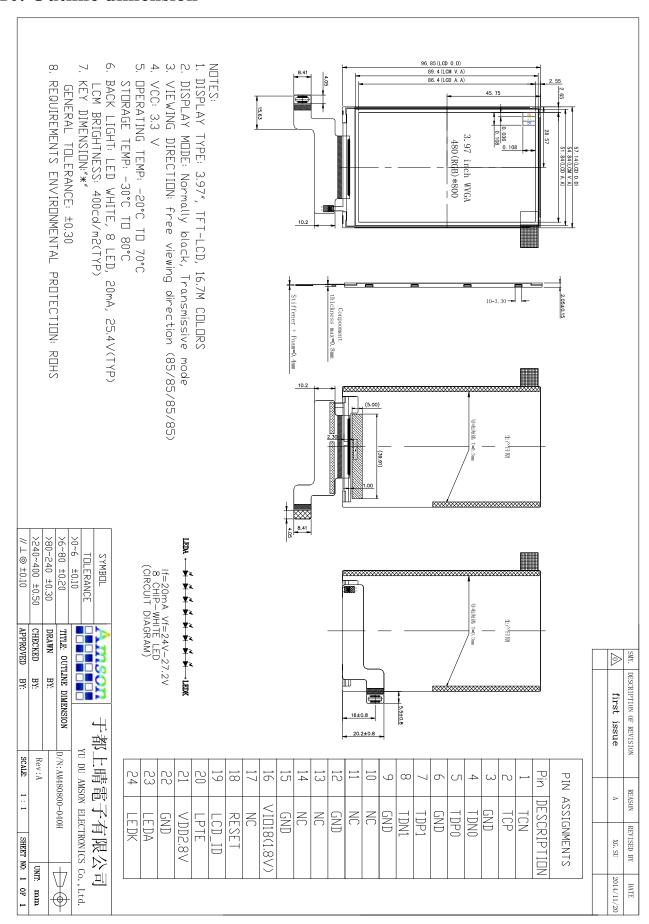

#### 10. Outline dimension

Version: A

2015-09-25

## 11. Table of Pin Assignment

### LCM Pin Assignment

| Pin | Symbol  | I/O      | Description                   | Remark |

|-----|---------|----------|-------------------------------|--------|

| No. |         | <b>-</b> | -                             |        |

| 1   | TCN     | I        | MIPI-DSI Clock Lane Negative  |        |

| 2   | TCP     | I        | MIPI-DSI Clock Lane Positive  |        |

| 3   | GND     | P        | ground                        |        |

| 4   | TDN0    | I        | MIPI-DSI Data Lane Negative 0 |        |

| 5   | TDP0    | I        | MIPI-DSI Data Lane Positive 0 |        |

| 6   | GND     | P        | ground                        |        |

| 7   | TDN1    | I        | MIPI-DSI Data Lane Negative 1 |        |

| 8   | TDP1    | I        | MIPI-DSI Data Lane Positive 1 |        |

| 9   | GND     | P        | ground                        |        |

| 10  | NC      | -        | No Connect                    |        |

| 11  | NC      | -        | No Connect                    |        |

| 12  | GND     | P        | ground                        |        |

| 13  | NC      | -        | No Connect                    |        |

| 14  | NC      | -        | No Connect                    |        |

| 15  | GND     | P        | ground                        |        |

| 16  | VDDIO   | I        | I/O PWOER                     |        |

| 17  | NC      | I        | No Connect                    |        |

| 18  | RESET   | I        | RESET Signal                  |        |

| 19  | LCD ID  | I        | LCD ID                        |        |

| 20  | LPTE    | О        | Tearing effect output pin     |        |

| 21  | VDD2.8V | I        | Power Supply                  |        |

| 22  | GND     | P        | ground                        |        |

| 23  | LEDA    | I        | LABAR Positive                |        |

| 24  | LEDK    | I        | LABAR Negative                |        |

Note 1: I/O---Input/Output; I---Input; P---Power/Ground

Version: A

2015-09-25

#### 12. MIPI-DSI interface

#### 12.1. General description

The communication can be separated 2 different levels between the MCU and the display module

-Interface Level: Low level communication

-Packet level: High level communication

#### 12.2. Interface level communication

#### 12.3.General

The display module uses data and clock lane differential pairs for DSI. Both clock lane and data lane0 can driven Low Power(LP)or High Speed(HS)mode. Data lane1 and Data lane2 can be driven High speed mode only.

|               | •                                   |                      |                 |

|---------------|-------------------------------------|----------------------|-----------------|

|               | Lane support mode                   | MPU(Host)            | OTM8009A(Slave) |

|               | Unidirectional lane                 | 1 N N +-             | <b>+</b>        |

| Clock<br>Lane | ★High-Speed Clock only              | PPI Lane Module      | Lane Module PPI |

|               | ★Simplified Escape Mode (ULPS Only) |                      |                 |

|               | Bi-directional lane                 | Д. <b>О-Р</b> НУ     | D-PHY L         |

| Data          | ★Forward high-speed only            | Lane Module          | Lane Module     |

| lane0         | ★Bi-directional Escape Mode         |                      |                 |

|               | ★Bi-direction LPDT                  | ()                   |                 |

|               | Unidirectional lane                 |                      | <b>•</b>        |

| Data<br>lane1 | ★Forward high-speed only            | D-PHY<br>Lane Module | Lane Module     |

|               | ★Simplified Escape Mode (ULPS Only) |                      |                 |

|               | Unidirectional lane                 | 1                    | <b>*</b>        |

| Data<br>lane2 | ★Forward high-speed only            | D-PHY<br>Lane Module | Lane Module     |

|               | ★Simplified Escape Mode (ULPS Only) |                      |                 |

Low Power mode means that each line of the differential pair is used in single end mode and a differential receiver is disable (A termination resistor of the receiver is disable) and it can be driven into a low power mode.

High Speed mode means that different modes and protocols in each mode when there are not used in the single end mode.

There are used different modes and protocols in each mode when there are wanted to transfer information from the MCU to the display module and vice versa.

The state Codes of the High Speed (HS)and Low Power(LP)lane pair are defined below.

| Lane Pair  | Line DC Voltage Levels |           | High Speed (HS) | Low-Pov      | ver (LP)    |

|------------|------------------------|-----------|-----------------|--------------|-------------|

| State Code | Dn+ Line Dn- Line      |           | Burst Mode      | Control Mode | Escape Mode |

| HS-0       | Low (HS)               | High (HS) | Differential-0  | Note 1       | Note 1      |

| HS-1       | High (HS)              | Low (HS)  | Differential-1  | Note 1       | Note 1      |

| LP-00      | Low (LP)               | Low (LP)  | Not Defined     | Bridge       | Space       |

| LP-01      | Low (LP)               | High (LP) | Not Defined     | HS-Request   | Mark-0      |

| LP-10      | High (LP)              | Low (LP)  | Not Defined     | LP-Request   | Mark-1      |

| LP-11      | High (LP)              | High (LP) | Not Defined     | Stop         | Note 2      |

Version: A

2015-09-25

## 13. Reliability

| Item<br>NO. | Test Item                         | Test condition                               | Description                                                                                         |

|-------------|-----------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 1           | High temperature operation        | Ta=70℃,240 h                                 | Endurance test applying the electric operation under high temperature for a long time               |

| 2           | Low temperature operation         | Ta=-20°C,240 h                               | Endurance test applying the electric operation under low temperature for a long time                |

| 3           | High temperature storage          | Ta=80°C,240 h                                | Endurance test applying the high storage temperature for a long time                                |

| 4           | Low temperature storage           | Ta=-30℃,240 h                                | Endurance test applying the low storage temperature for a long time                                 |

| 5           | High temperature<br>High humidity | Ta=60°C,<br>90%RH,240 h                      | Endurance test applying electric operation under high temperature and high humidity for a long time |

| 6           | Temperature Cycle                 | -30°C (30min),<br>+80°C (30min)<br>200cycles | Endurance test applying the low and high temperature cycle  One cycle                               |

| 7           | Shock Test                        | 100G ,6ms<br>Direction: X,Y,Z<br>3 times     | Measure an aerospace product's response to mechanical shock                                         |

Version: A

2015-09-25

14. packaging TBD